前回の続きで、zcu106のPCI ExpressのTRDを見て行こうと思う。最初に、PCI Expressの規格を調べてみよう。と言っても規格書は、ネットには落ちていないので、wikipediaから調べる。

https://ja.wikipedia.org/wiki/PCI_Express

最初に物理的配線を確認する。

各PINを想像してみる。RC側(例えばPC側)から見たイメージで説明を書いてみる。

| PIN | Side | Name | |

| 1 | A | PRSNT1# | Cardが接続中か確認するPIN |

| 1 | B | +12V | 電源 |

| 4 | A | Ground | グランド |

| 5 | A | TCK | JTAG用 |

| 5 | B | SMCLK | SM Bus。たぶん、補助通信用 |

| 6 | A | TDI | JTAG用 |

| 6 | B | SMDAT | SM Bus。たぶん、補助通信用 |

| 7 | A | TDO | JTAG用 |

| 8 | A | TMS | SM Bus。たぶん、補助通信用 |

| 8 | B | +3.3V | 電源 |

| 9 | B | TRST# | JTAG用 |

| 10 | B | +3.3V aux | aux用電源。 |

| 11 | A | PERST# | リセット。RC側がカードをリセットする信号。 |

| 11 | B | WAKE# | 電源復帰。パワーセーブ時に、復帰したことを通知する? |

| 12 | B | CLKREQ# | クロック要求。カード側がクロックを要求する時か? |

| 13 | A | REFCLK+ | 基準クロック差動+。 |

| 14 | A | REFCLK- | 基準クロック差動ー。 |

| 14 | B | HSOp(0) | レーン0 送信。差動+。 |

| 15 | B | HSOn(0) | レーン0送信。差動ー。 |

| 16 | A | HSlp(0) | レーン0受信。差動+ |

| 17 | A | HSln(0) | レーン0受信。差動ー。 |

x1のところまで、見てみた。x4、x16とレーンが増えていくが、基本は、PRSTとレーンの信号が追加されるだけだ。

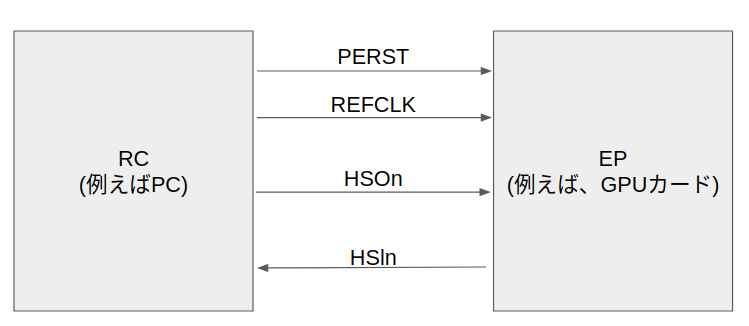

補助的なところと、パワーセーブを除くと、REFCLKとHSOp、HSlp、PERSTが重要な信号だと思う。

電源等を除くと、論理的には、以下のブロック図だと思う。