Build a PCIe model of the zcu106 Target Reference Design (TRD) for studying PCIE. TRD is described on the following page. Today’s content is the same as the content on this page.

First, download the TRD code. Download from the link below.

https://www.xilinx.com/cgi-bin/docs/ctdoc?cid=bigfile;d=rdf0428-zcu106-vcu-trd-2020-2.zip

After downloading, unzip it in an appropriate directory.

unzip zcu106-vu-trd-2020.2.zipThen change to the pl directory of the unzipped directory

cd rdf0428-zcu106-vcu-trd-2020.2/plSet the Vivado environment variables. The scripts that set the environment variables may be different.

source /tools/Xilinx/Vivado/2020.2/setting.shNext, perform the PCIE design. Vivado launches and opens the PCIE design.

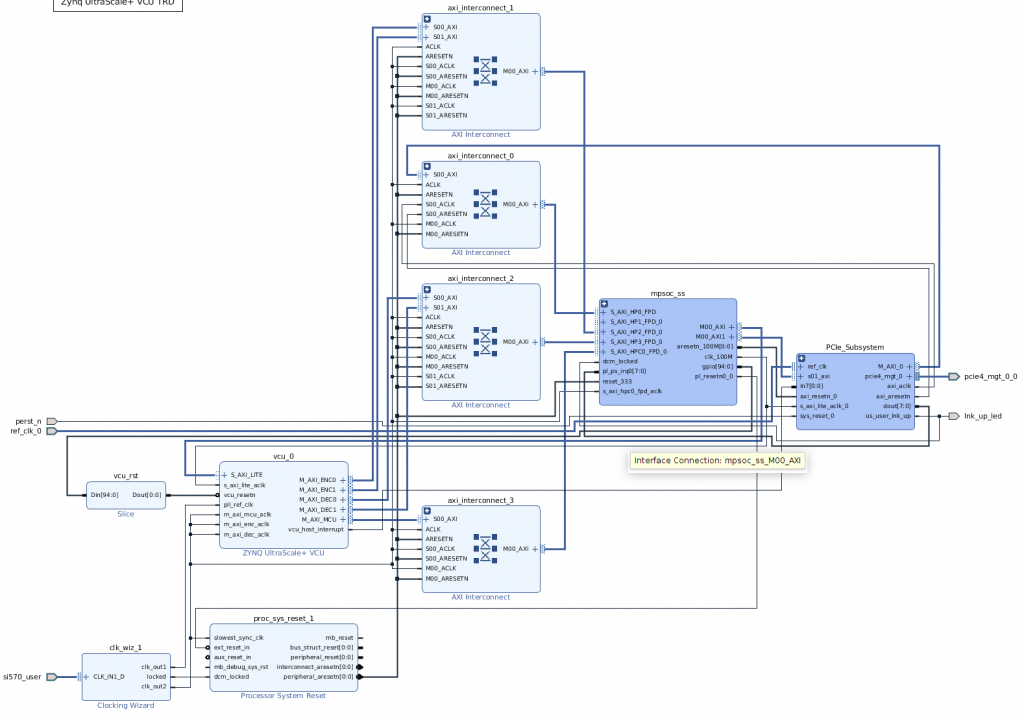

vivado -source designs/zcu106_pcie/project.tclAfter running tcl, you can see a design like this.

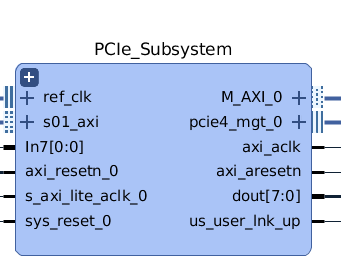

This design includes PCIE and Video Codec. The PCIE part becomes the PCIe_Subsystem part. Click the “+” in the upper left of PCIe_Subsystem to see the details.

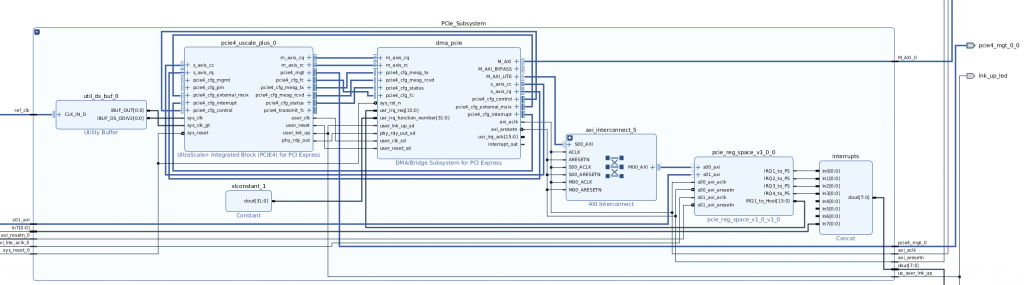

I think you will see a design like this when you open it.

It looks difficult because there are 5 blocks, but the two important ones are UltraScale + Integrated Blcok (PCIE4) for PCI Express and DMA / Bridge Subsystem for PCI Express. However, even if I tried to make the same composition myself, I couldn’t.

Then run Build. If you click Generate Bitstream of Vivadoe as it is, Build will start. Please note that the zcu106 requires 16GB or more of memory on the PC in the development environment.