PCIEの勉強のために、zcu106のTarget Reference Design(TRD)のPCIEのモデルをビルドする。TRDは、以下のページで説明されている。今日の内容は、このページの内容そのままだ。

最初に、TRDのコードをダウンロードする。以下のリンクからダウンロードする。

https://www.xilinx.com/cgi-bin/docs/ctdoc?cid=bigfile;d=rdf0428-zcu106-vcu-trd-2020-2.zip

ダウンロードしたら適当なディレクトリで解凍する。

unzip zcu106-vu-trd-2020.2.zip次に、解凍したディレクトリのplディレクトリに移動する

cd rdf0428-zcu106-vcu-trd-2020.2/plVivadoの環境変数を設定しておく。環境変数を設定するスクリプトは、各自異なるかもしれない。

source /tools/Xilinx/Vivado/2020.2/setting.sh次に、PCIEのデザインを実行する。Vivadoが起動してPCIEのデザインが開かれる。

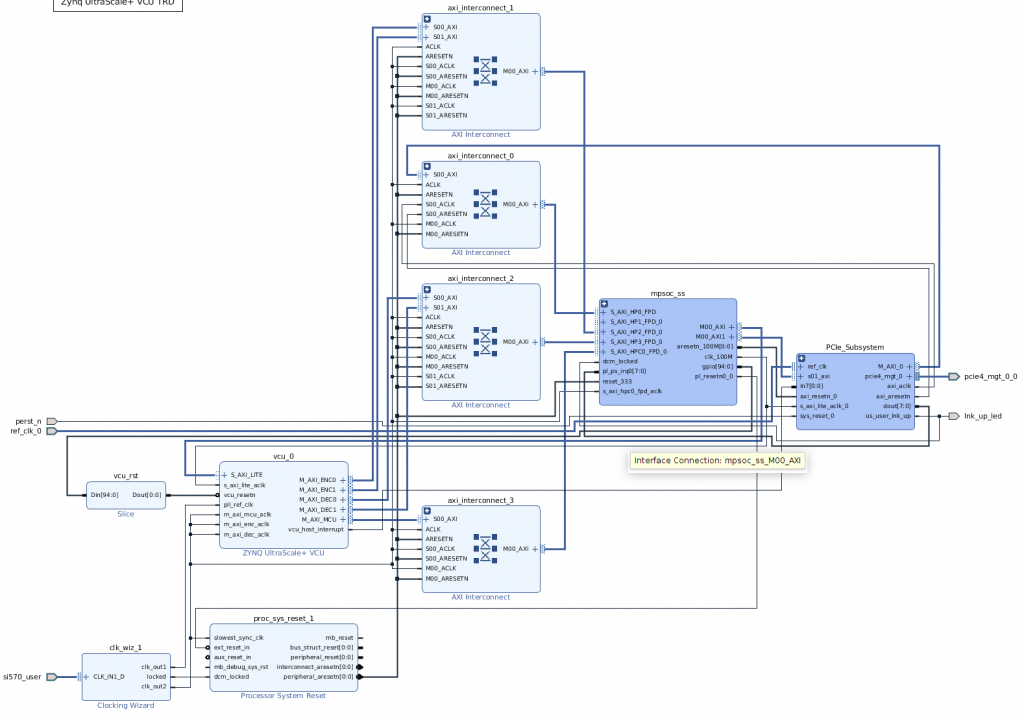

vivado -source designs/zcu106_pcie/project.tcltclを実行後に、このようなデザインがみえる。

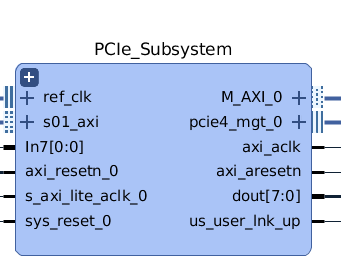

このデザインは、PCIEとVideo Codecを含まれている。PCIEの部分は、PCIe_Subsystemの部分になる。PCIe_Subsystemの左上の”+”をクリックすると詳細が表示される。

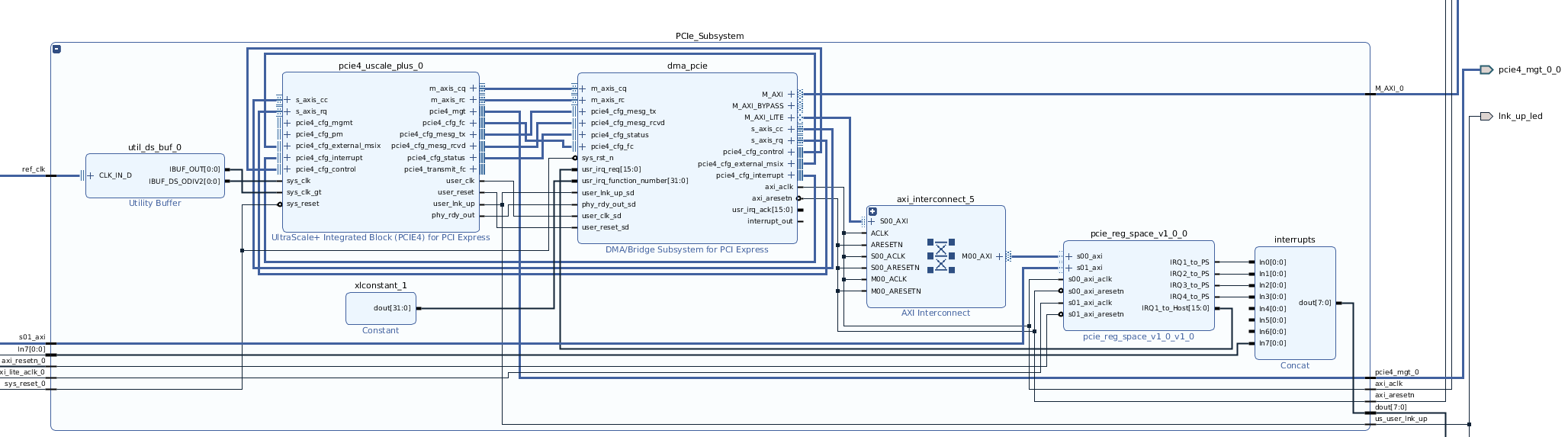

開いくとこのようなデザインが表示されると思う。

5個のブロックがあるので、難しく見えるが、大事なのは、UltraScale+ Integrated Blcok(PCIE4) for PCI Expressと、DMA/Bridge Subsystem for PCI Expressの2つだ。しかし、自分で、同じ構成を作ろうと思っても作れなかった。

次に、Buildを実行する。このまま、VivadoeのGeneerate Bitstreamをクリックすると、Buildが始まる。zcu106は、開発環境のPCのメモリが16GB以上必要になるので、注意が必要だ。