DPUを使ったPlatformを作りたいと思った。

以下にQiitaの記事がありますが、Vivadoのバージョンが2019.2で、自分の環境と異なる点や、記事に添付されているTCLで読み込みましたが、力不足で、読み込めなかったので、記事を参考にしながら、2021.2で作りました。

VivadoのPJを作っただけでVitis AIの動作確認は行っていません。

https://qiita.com/mmitti/items/3c7e85c845219ee392b0

DPU IP Download

DPUのIPは、デフォルトのレポジトリに格納されていなく、Xilinx Vitis AIのgitからダウンロードしておく必要がありそうです。

git clone --recurse-submodules https://github.com/Xilinx/Vitis-AI Vivadoの取り込み

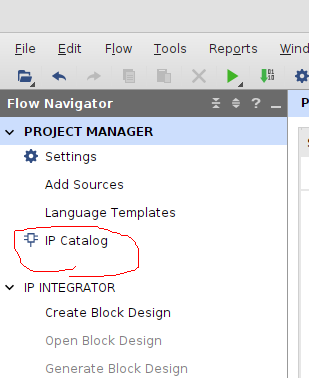

Vivadoに取り込むためには、まずは、IP Catalogを開きます

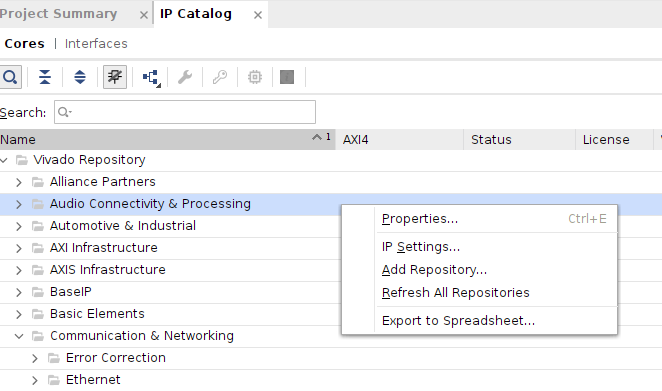

IP CatalogのWindow上で、右クリックして、Add Repositoryを選択します

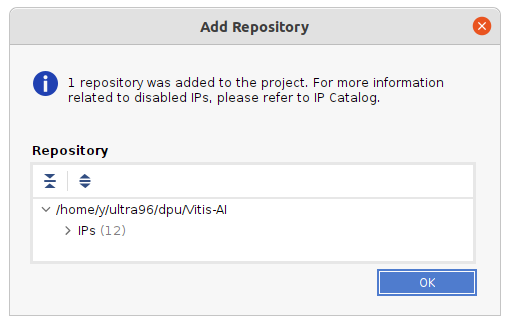

そして、先程git cloneしたVitis AIのディレクトリを選択

そうすると、IPがあったことを知らされます。OKをクリックします。

これで、Add IPからDPUを選択できるようになりました。

あとは、Qiiitaの記事のように、IPをBlock Desgin上に配置して、線をつなげていけばできるはずです。

いくつか設定が必要なIPがあったので説明します。

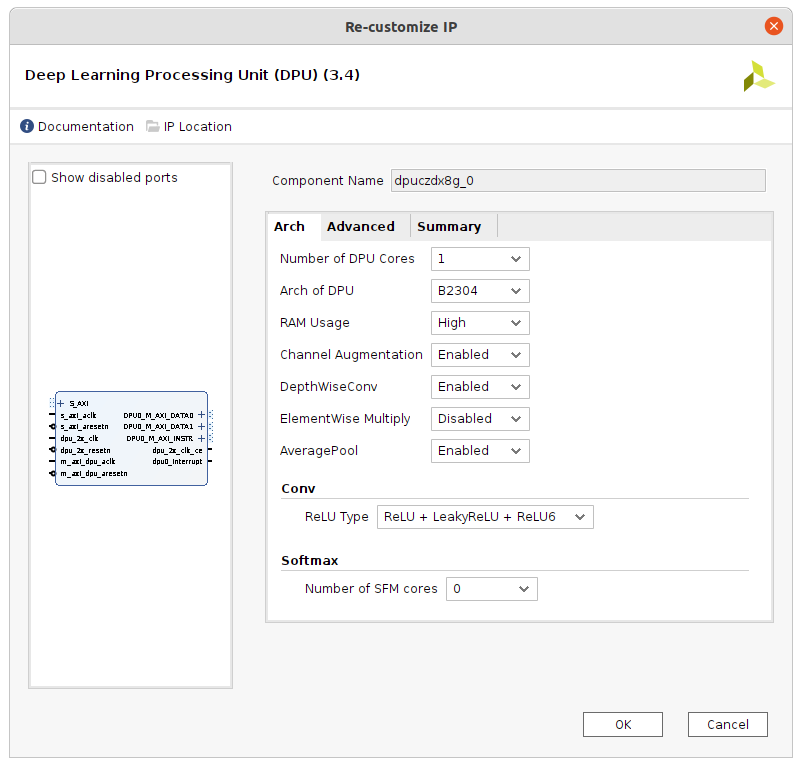

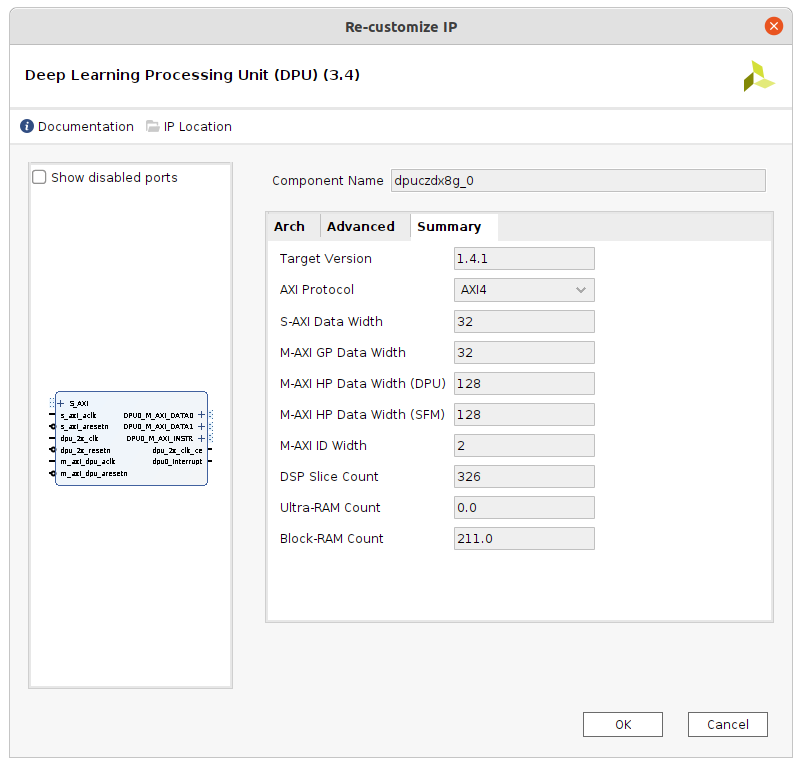

DPU

DPUは、Ultra96だとリソースに余裕がないため、デフォルトのままだとエラーになります。

Qiitaの記事のTCLファイルを参考にして、DPUの設定を行います

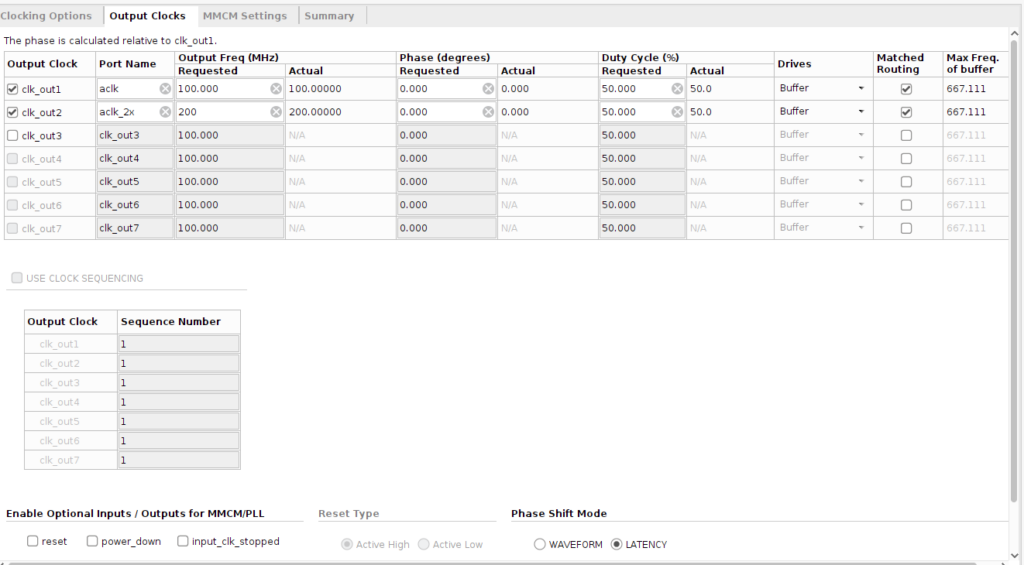

Clocking wizard

dpuのDSPには2倍のClockが必要ということで、Clocking Wizardの設定を行います。記事にも書かれていますが、DPUのクロックは同期が必要ということで、Matched Routingにチェックをいれます

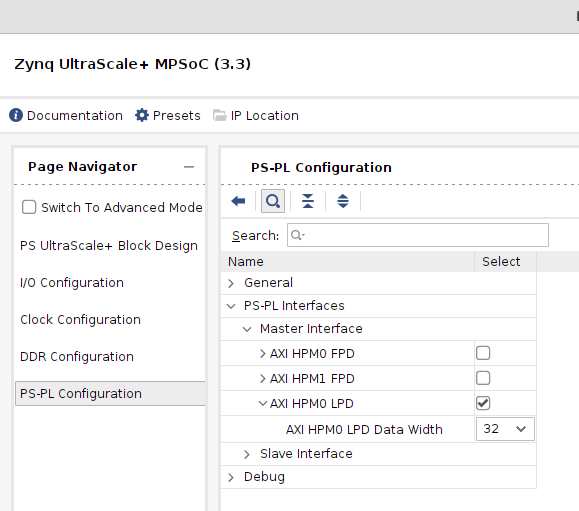

Zynq UltraScale+ MPSoc

記事の画像を見て、IP同士をつなげていきますが、DPUのSlave IFは、32bit幅ですので、そこは設定を変更する必要があります。AXI HPM0 LPD Data Widthを32にします。

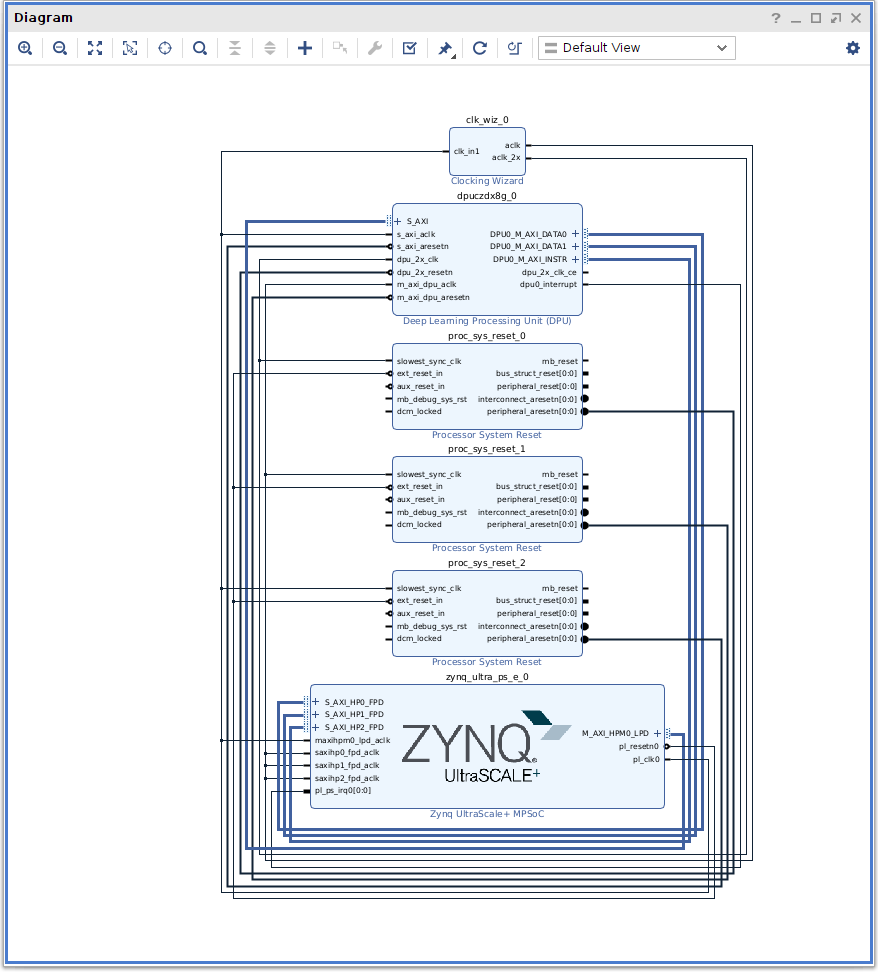

Block desgin

生成したBlock desginになります

ソースコード

作成したPJは以下のおいてります