zcu106で、PCI Express のEnd Pointを実装してみた。Vivadoでビルドするまでになります。(動作確認しておらず)

Vivadoでプロジェクトを作成していきます。

Nextをクリック

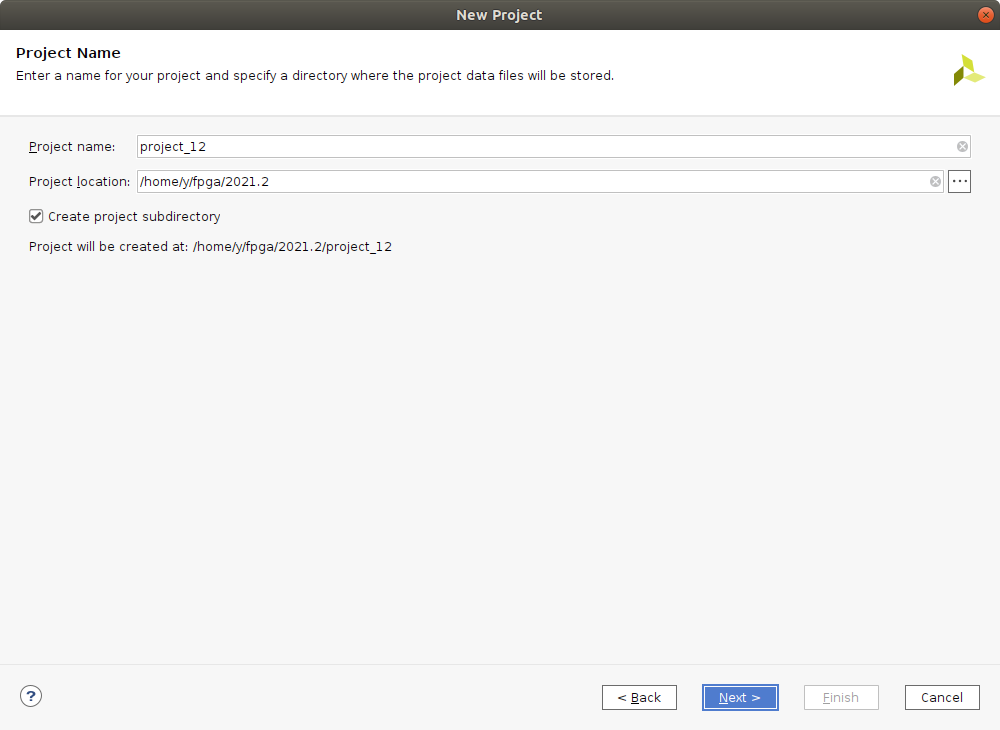

プロジェクト名と保存ディスプレイを選択して、Nextをクリック

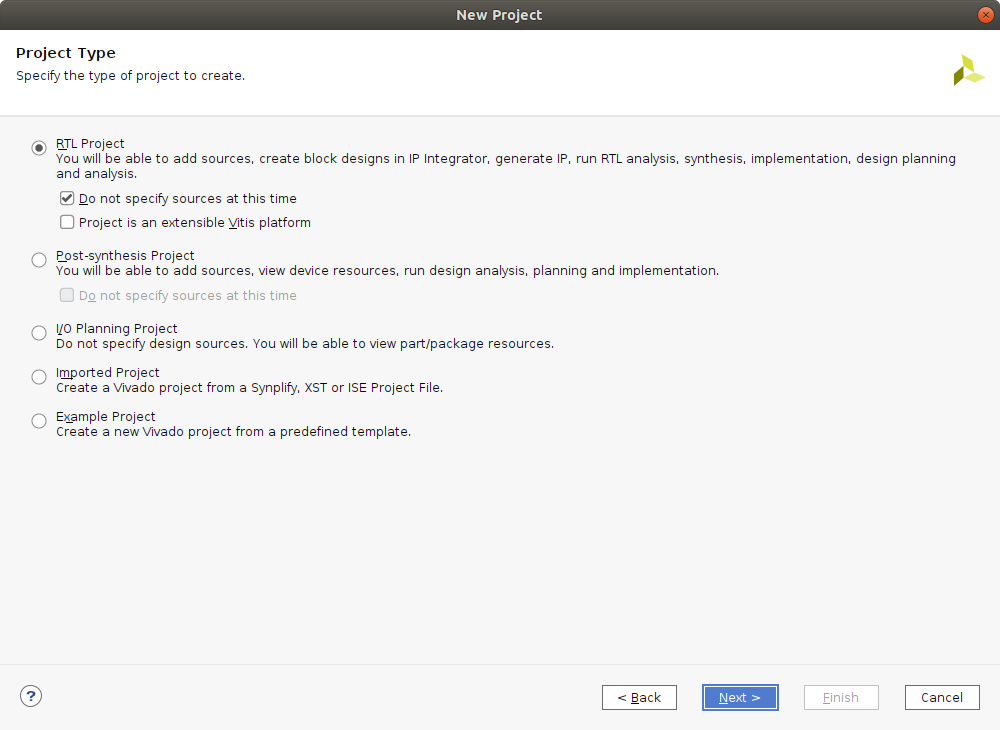

RTL Projectを選択してクリック

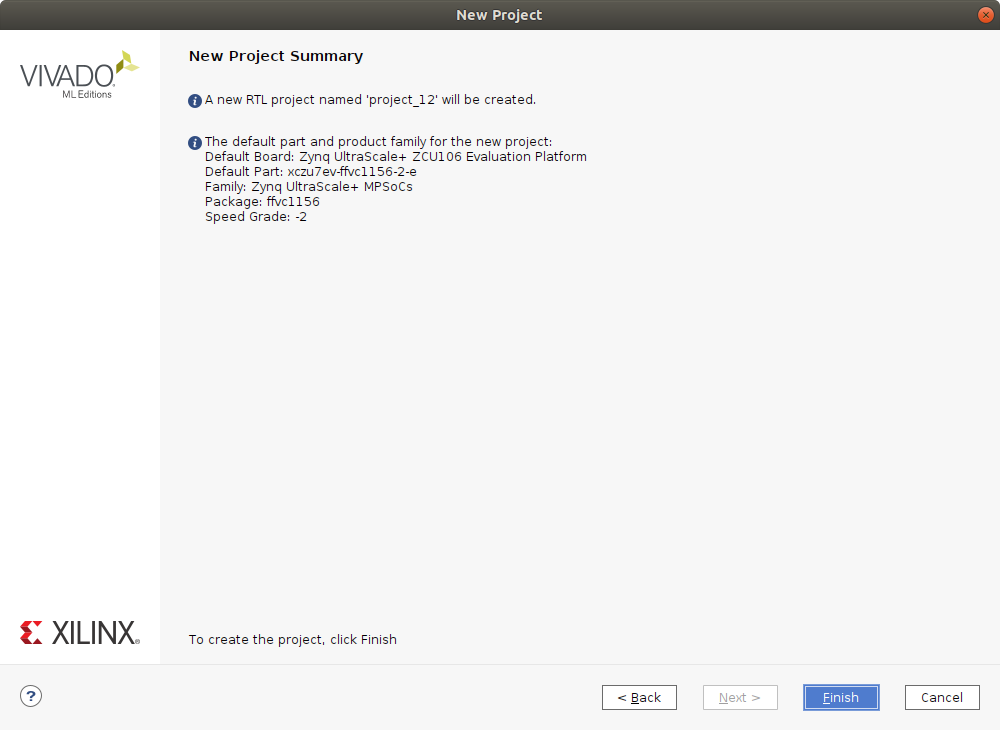

Boardsで、zcu106を検索して、Nextをクリック

Summaryを確認して、Finishをクリック

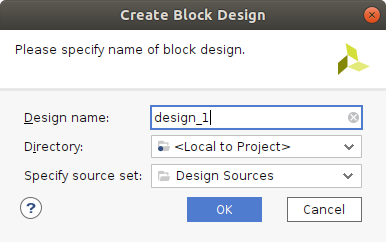

PROJECT MANAGERから、Create Blcok Desginをクリックして、OKをクリック

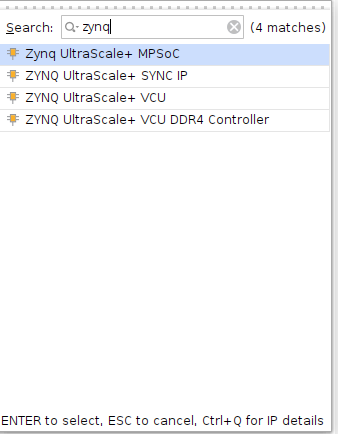

Diagramで+をクリックして、検索窓からzynqで、検索して、Zynq UltraScale+ MPSoCをダブルクリックします。

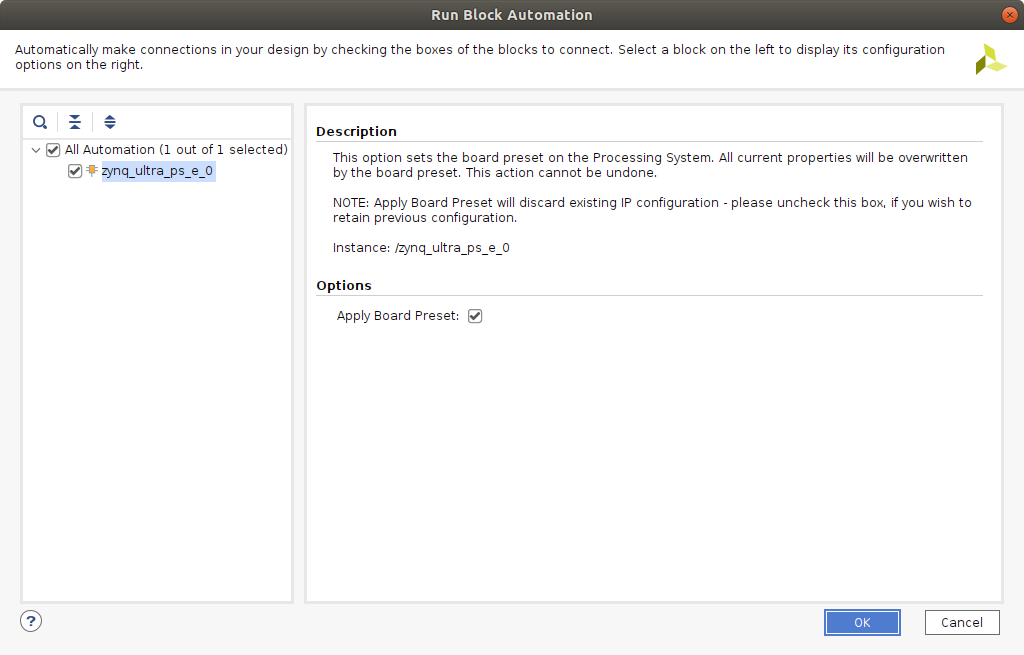

Run Block Automationをクリックして、OKをクリックします。

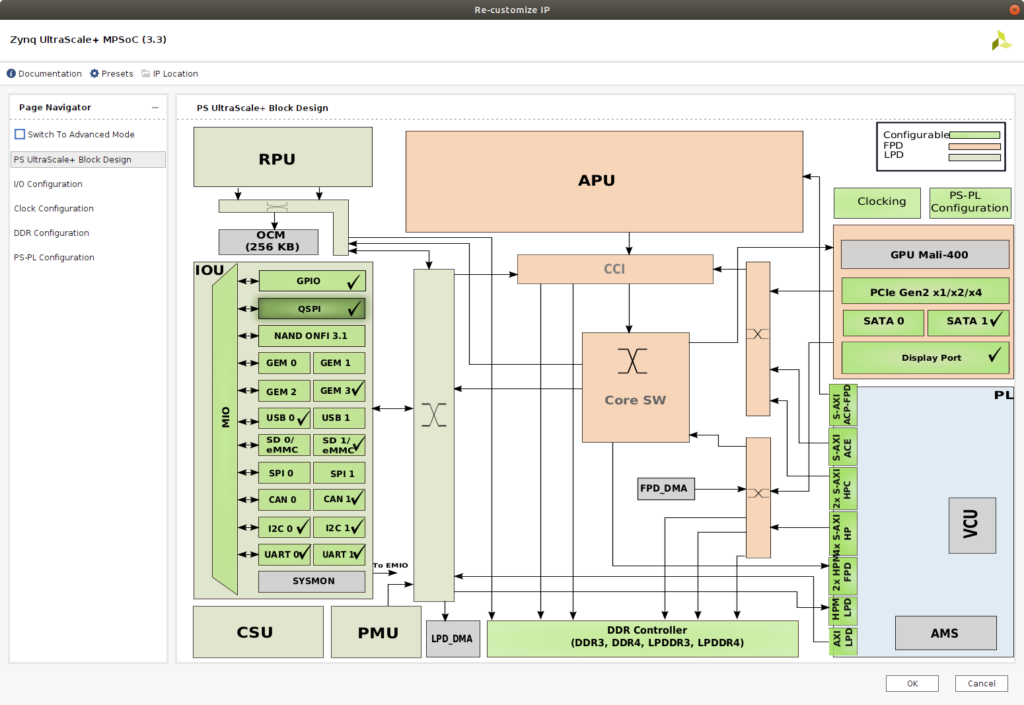

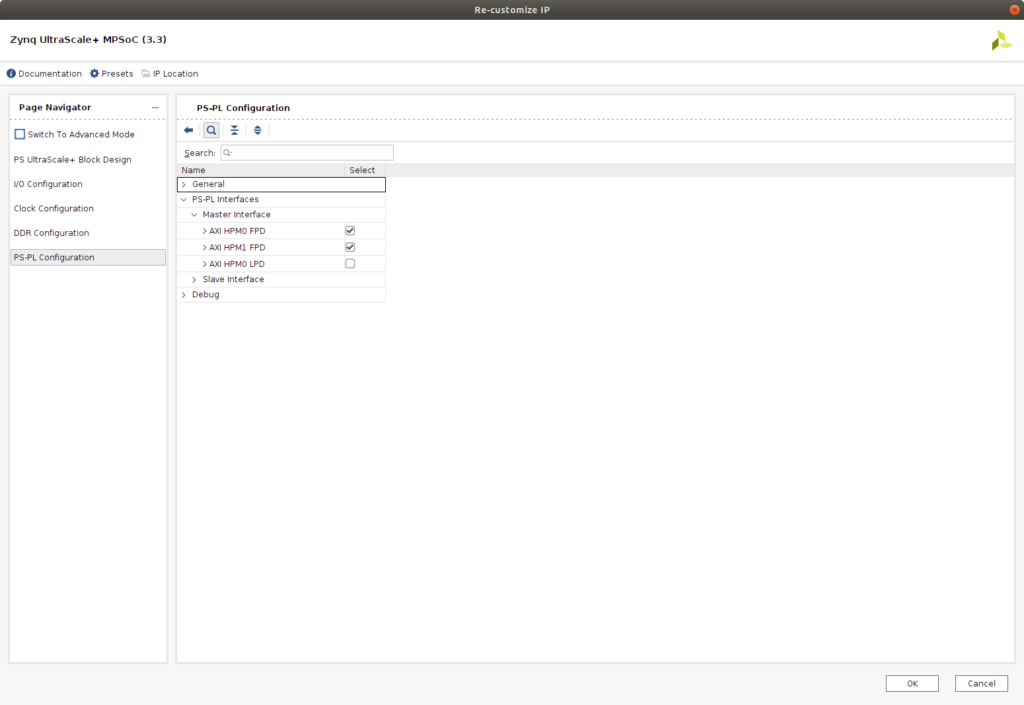

ZYNQをダブルクリックして、Re-customize IP画面を表示します。

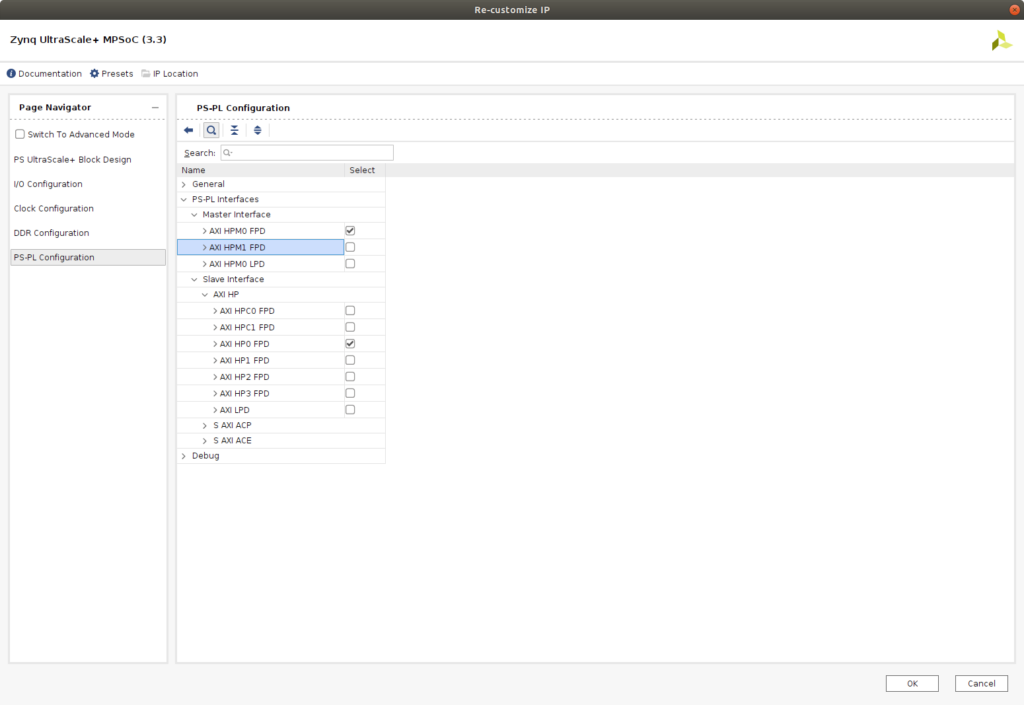

PS-PL Configuration→PS-PL Interface->Master Interfaceをクリックをして、AXI HPM1 FPDのチェックを外します。

(AXI HPM0 FPDがチェックされた状態です)

PS-PL Configuration→PS-PL Interface->Slave Interfaceをクリックをして、AXI HP0 FPDをチェクします。OKをクリックします。

Zynq UltraScale+ MPSoCの状態です。

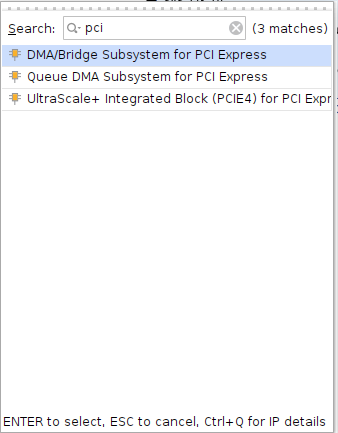

BLOCK DESGINのDiagramで、+ボタンをおし、pciで検索し、DMA/Bridge Subsystem for PCI Expressをクリックします。

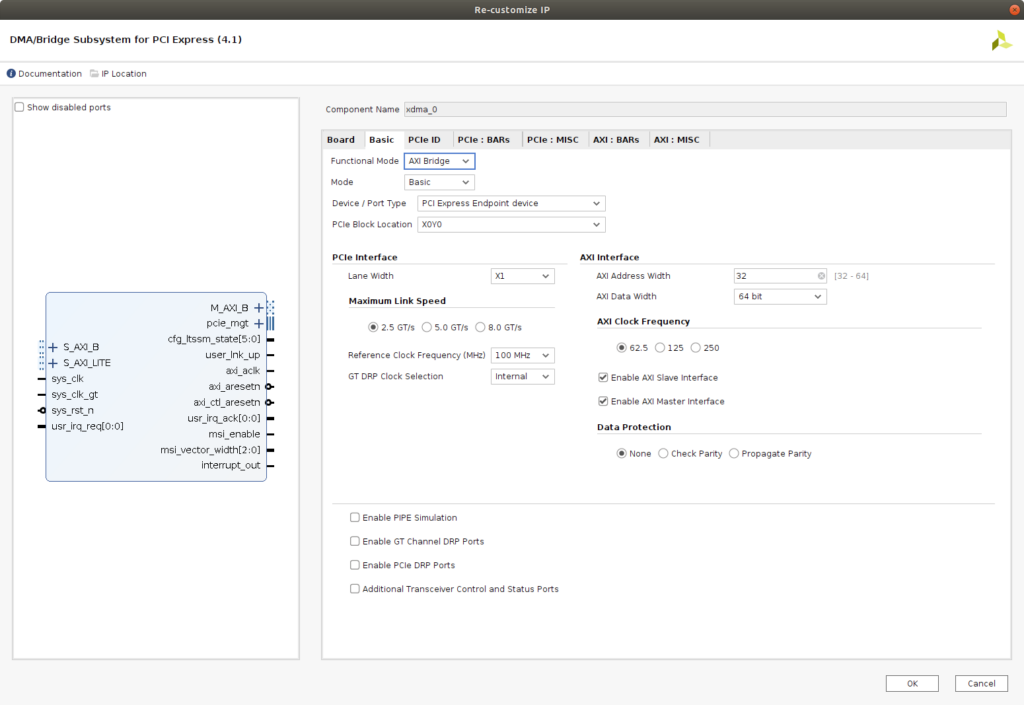

DMA/Bridge Subsystem for PCI Expressをダブルクリックして、re-custamize IPを表示します。BasicのタグでFUnctional Mode AXI Bridge にします。OKをクリックします。

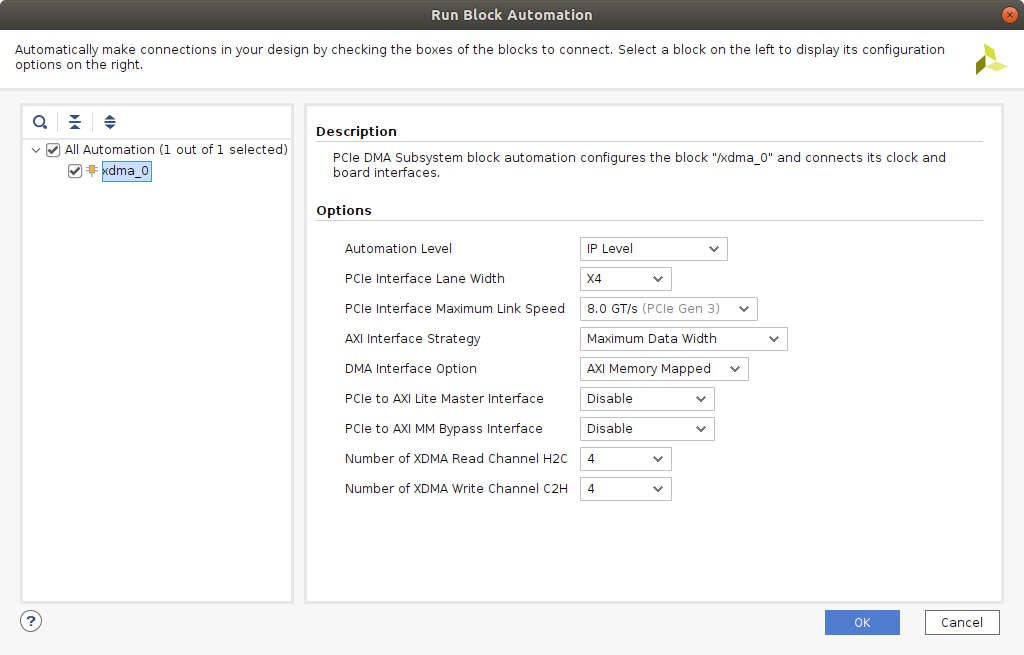

Run Blcok Automationをクリックします。OKをクリックします。

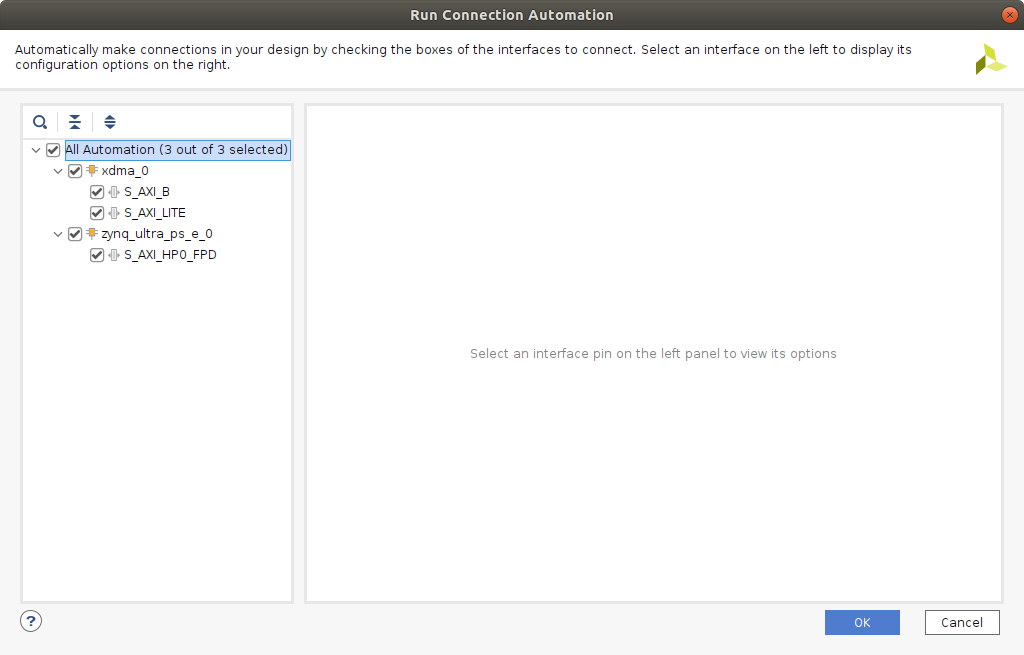

Run Connection Automationをクリックします。All Automationをチェックして、OKをクリックします。

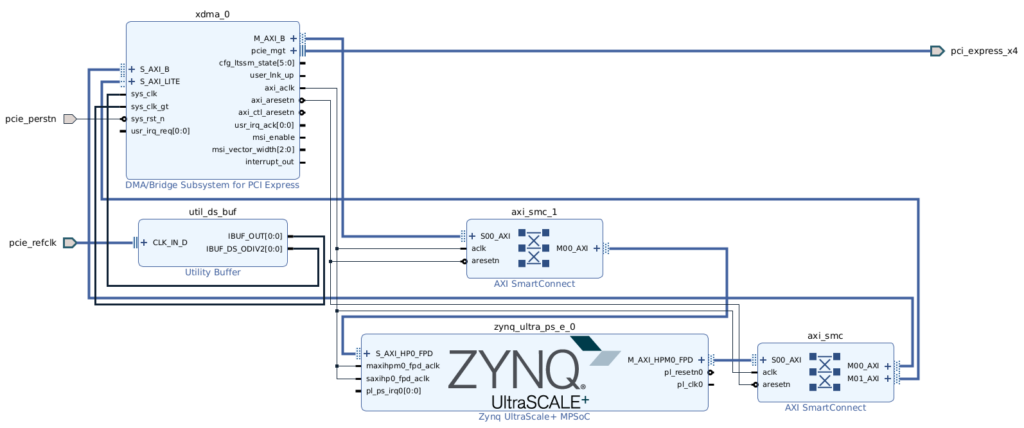

今のDiagramの状態です。

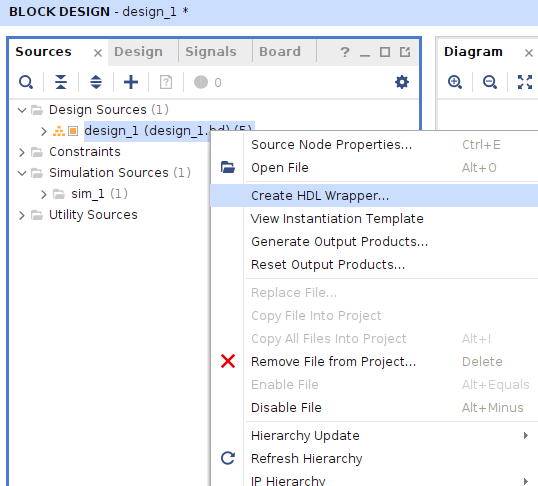

BLOCK DESGIN->Source->Hierarchy->Desgin Sourcesのdesgin_1(design_1.bd)を右クリックして、Create HDL Wrapperをクリックして、OKをクリックします。

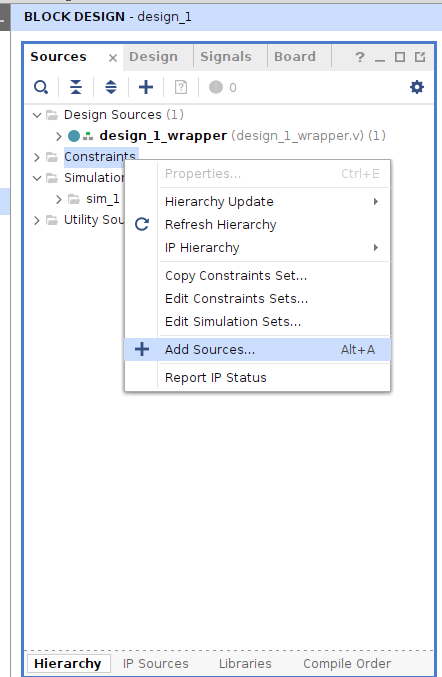

BLOCK DESGN->Sources->Constraintsで右クリックし、Add Sourcesをクリックします。

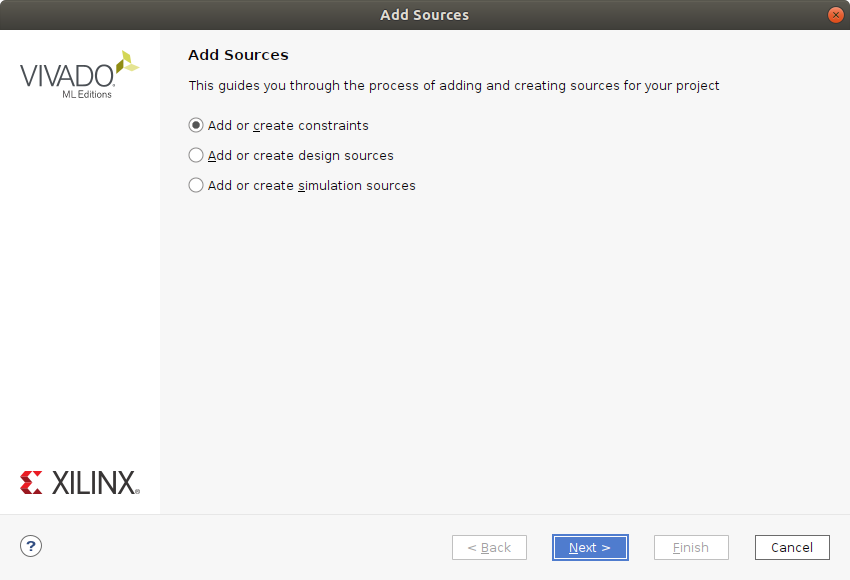

Add or create constraintsを選択して、Nextをクリックします。

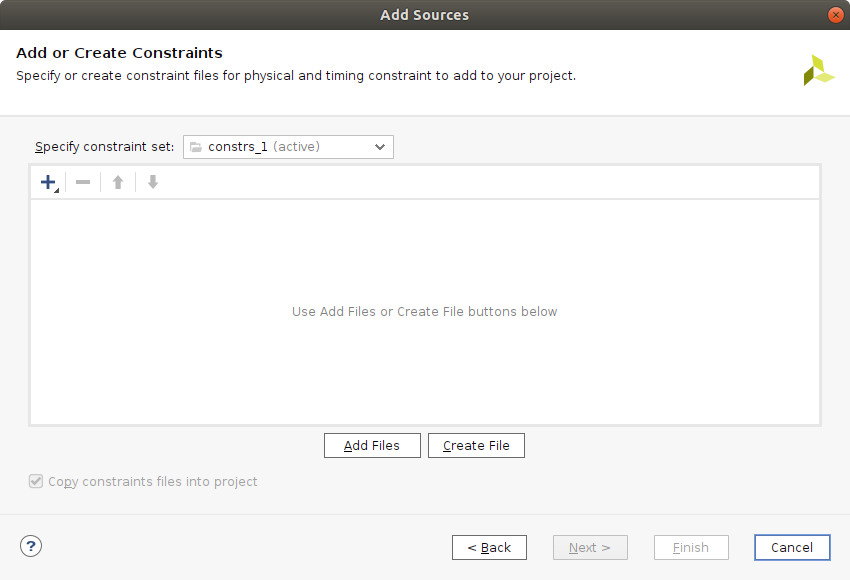

Creatte Fileをクリックします。

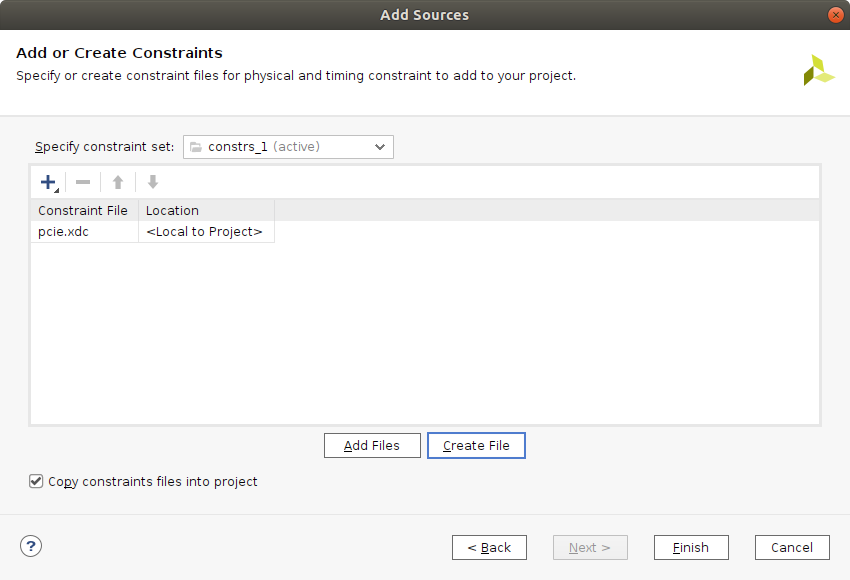

File名として、pcie.xdcを入力して、OKをクリックします。

Finishをクリックします。

BLOCK DESGIN->Sources->Constraintsから、pcie.xdcをクリックしてテキストエディタを開きます。そして、以下のように制約ファイルを作成します。

set_property PACKAGE_PIN AD4 [get_ports {pci_express_x4_txp[0]}]

set_property PACKAGE_PIN AE6 [get_ports {pci_express_x4_txp[1]}]

set_property PACKAGE_PIN AG6 [get_ports {pci_express_x4_txp[2]}]

set_property PACKAGE_PIN AH4 [get_ports {pci_express_x4_txp[3]}]

set_property PACKAGE_PIN AE2 [get_ports {pci_express_x4_rxp[0]}]

set_property PACKAGE_PIN AF4 [get_ports {pci_express_x4_rxp[1]}]

set_property PACKAGE_PIN AG2 [get_ports {pci_express_x4_rxp[2]}]

set_property PACKAGE_PIN AJ2 [get_ports {pci_express_x4_rxp[3]}]

# ref_clk

#set_property PACKAGE_PIN AF12 [get_ports {ref_clk_clk_p[0]}]

set_property PACKAGE_PIN AB8 [get_ports {pcie_refclk_clk_p[0]}]

set_property PACKAGE_PIN L8 [get_ports pcie_perstn]

set_property IOSTANDARD LVCMOS18 [get_ports pcie_perstn]

Flow Navigator->PROGRAM AND DEBUG->Generate Bitstreamをクリックする。

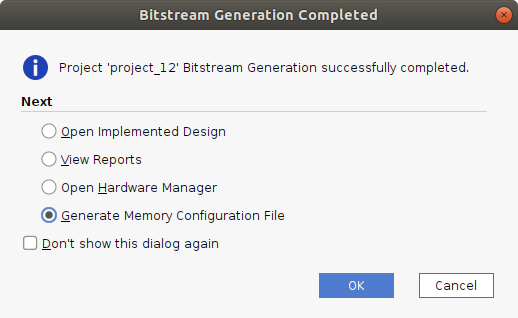

成功とすると、Bistream Generation Completedの画面が表示される

結果は、以下のリンクに保存してある