VitisとVivadoを使ったデバックです。

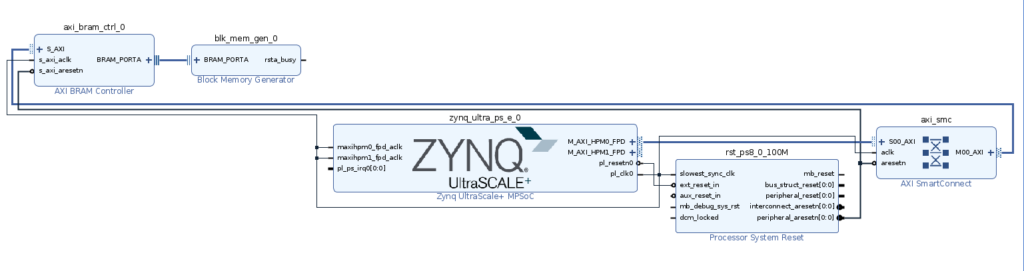

デバック対象は、Blcok Memory Generatorを接続して、Block Memroyにアクセスする箇所をILAで観測します。

Vivadoの準備

対象のブロック図です。

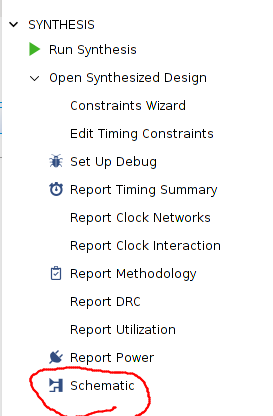

SYNTHESIS Open Synthesized DesignをOpenして、Schematicを開く。つまり、事前に、Run Synthesisを済ましておく。

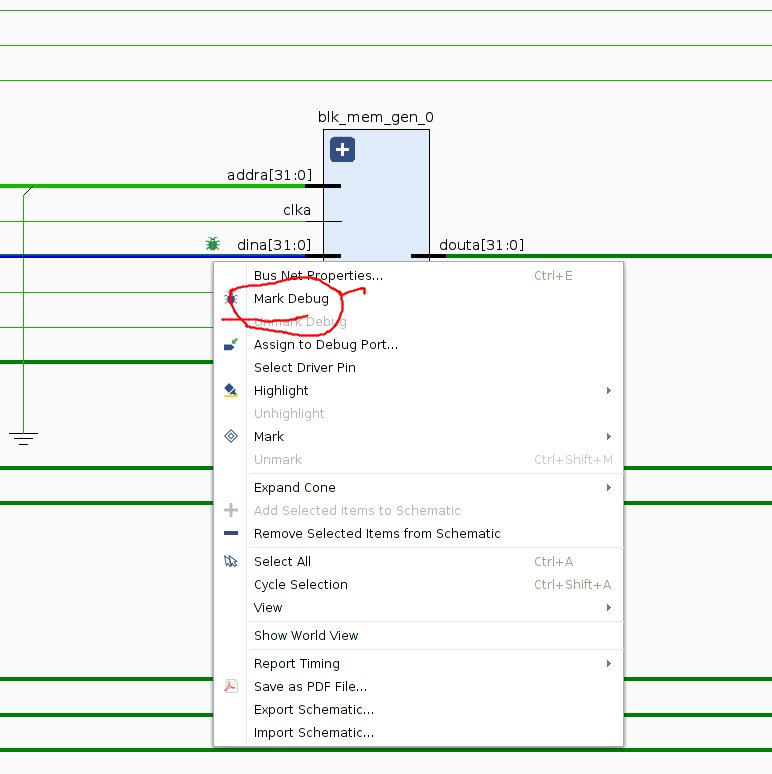

Schematicを開いて、Block Memory Generatorのdinaと、weaを選択して右クリックして、Mark Debugを選択する。選択すると、線の上に、蜘蛛のマークがつく。

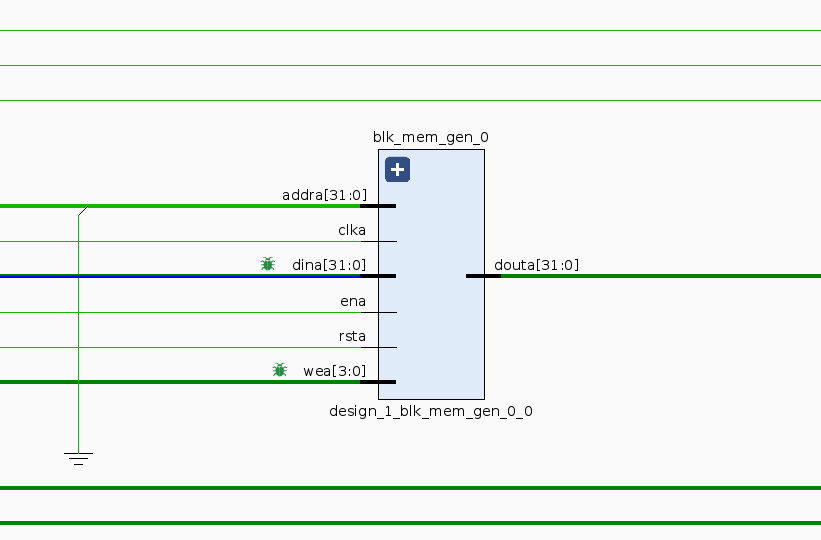

dinaとweaにMark Debugした結果だ。ZynqのCPUから、Block Memoryにワイトした時に、ILAを観測できるようになるつもりだ。

次に、SYNTHESIS Open Synthesized Design Set Up Debugをクリックする。Nets To Debugで、ILAと接続しようとしている線が選択されていることを確認する。また、Clock Domainが選択されていない場合は、観測に使用するClockを選択する。

ちなみに、観測するClockと同等のClockは観測できないので注意が必要だ。

Nextを押していくと、最後は、ファイルに保存するように、指示される。保存したファイルは、Source Constraintsに、現れる。

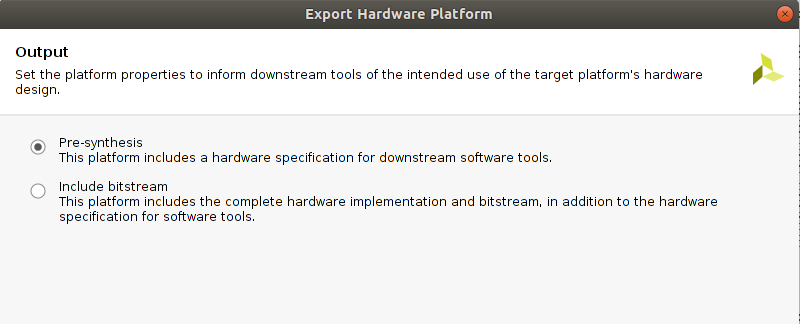

次に、この状態で、Generate BitStreamを行う。完了したら、HardwareをExportする。File→Export→ Export Hard wareで、Outputは、Pre-synthesisを選択する。いつもは、include bitstreamを選択しているので、ここがちょっと違う。

これで、Vivado側の準備は終わったので、Vitis側の準備をする

Vitisの準備

プログラム的には、0xa0000000〜にBlock Memoryが割り当てられているので、そこに0xaaaa5555をライトするプログラムを用意する。

u32 *ptr;

ptr = 0xa0000000;

xil_printf("%x %x\n\r", ptr , *ptr);

*ptr = 0xaaaa5555;

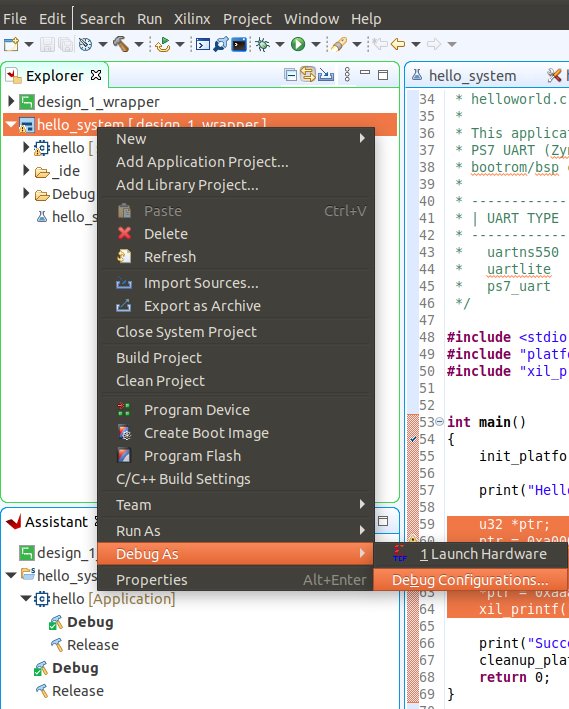

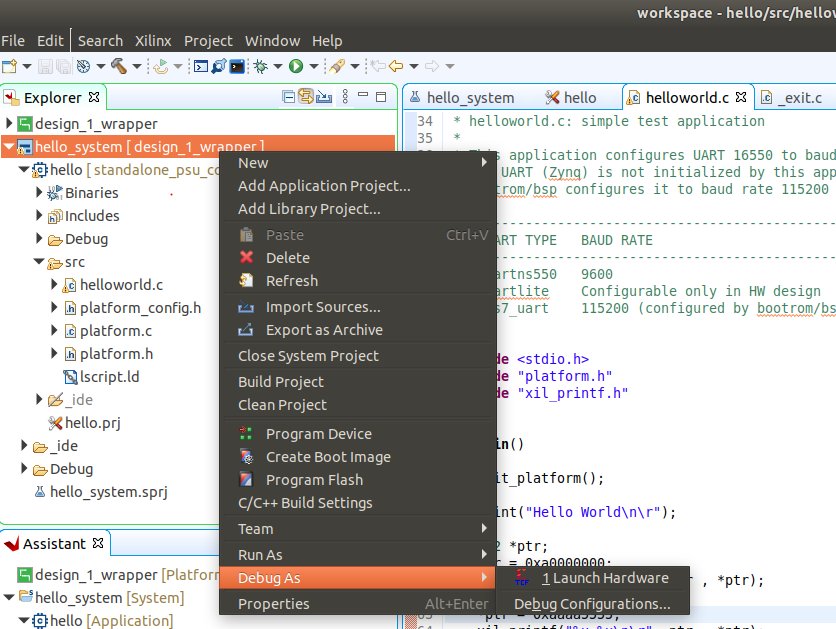

xil_printf("%x %x\n\r", ptr , *ptr);Vitisでは、Systemを右クリックして、Debug As →Debug Configrationを選択する

もし設定がない場合は、New Configrationで、設定を作成する必要があったと思う。

Target Setupの画面を開く。左下のところで、Reset entire system, program FPGAが選択されていないことを確認して、ApplyしてCloseをクリックする。

Vitisでアプロを起動する前に、VivadoでProgram Deviceするので、Vitisでは、Resetしない。VivadoでProgram Deviceするので、VitisではProgram FPGAはしないというわけだ。

ここまで、準備は整ったので、デバックしてみる。

電源On

基板の電源を入れる。

Vivadoの実行

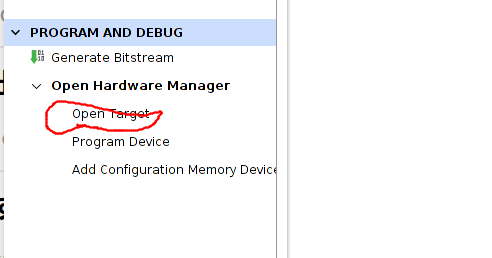

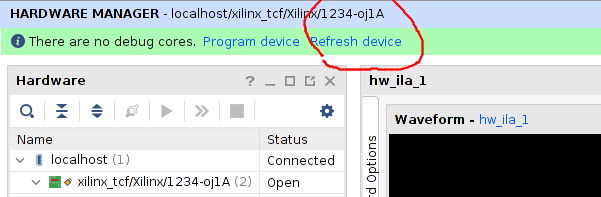

Open Hardware Managerをクリックして、Open Targetする。Auto Connectすると、JTAGで接続された基板と接続できると思う。

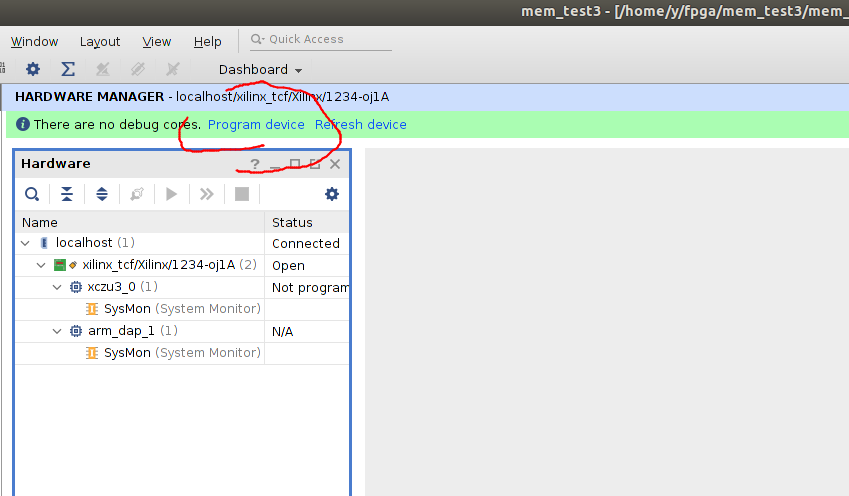

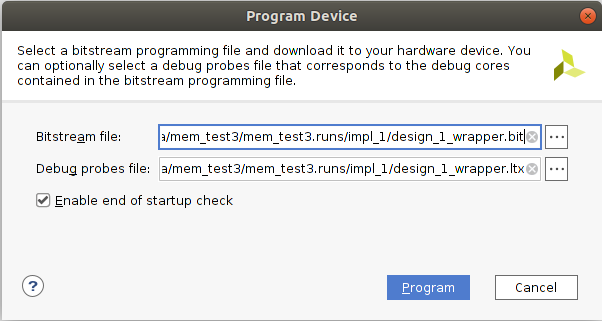

そして、Program Deivceをクリックして、生成されたbitとltxファイルを基板に転送する

転送するファイルを選択する。普通にしてたら、デフォルトで選択されているはずだ。

Vitisで実行する

次に、Vitis側を実行する。Systemを右クリックして、Debug As右Launch Hardwareを選択する

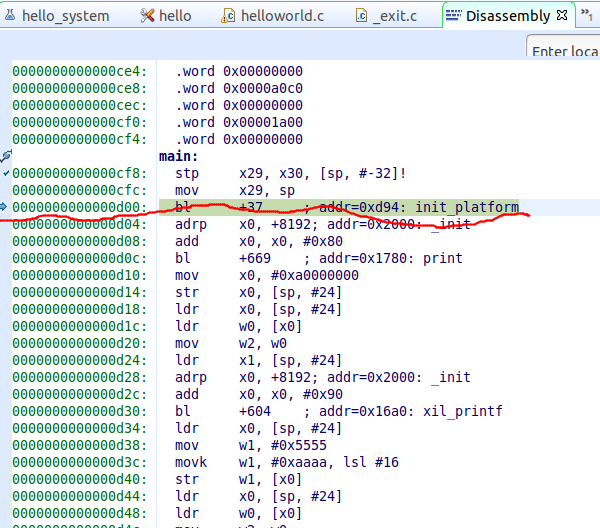

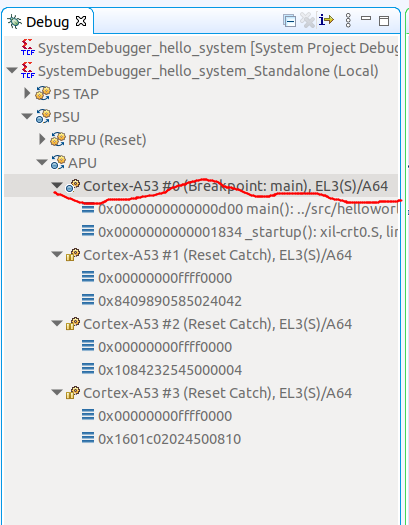

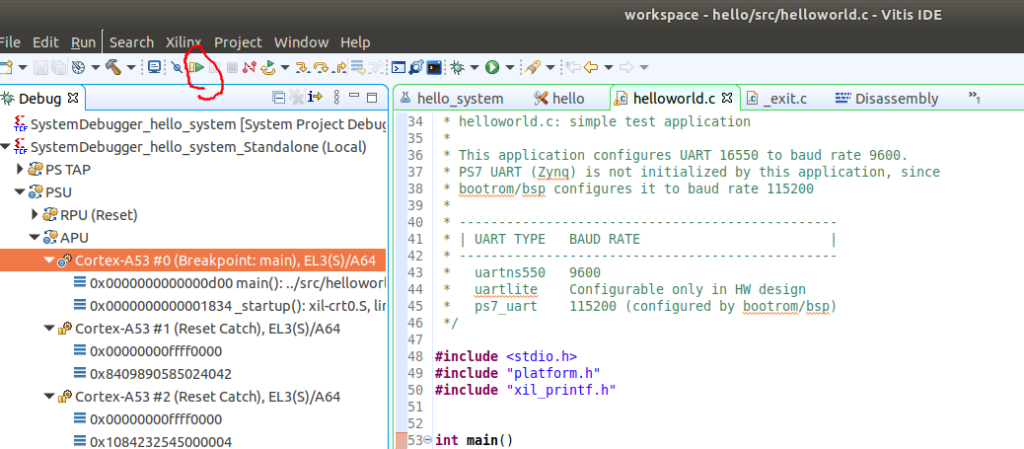

そうすると、Vitisが動き初めて、CPUを実行し、デフォルトだと、main関数の先頭にあるbreak pointでブレイクした状態で、止まる。このbreak pointは自分で設定しなくても設定されていると思う。

CPUの状態もBreakpointで止まっているのがわかる

Vivadoでトリガーをかける

次に、Vivadoで、ILAのトリガーをかける

Vivadeで、Refresh deviceをクリックする

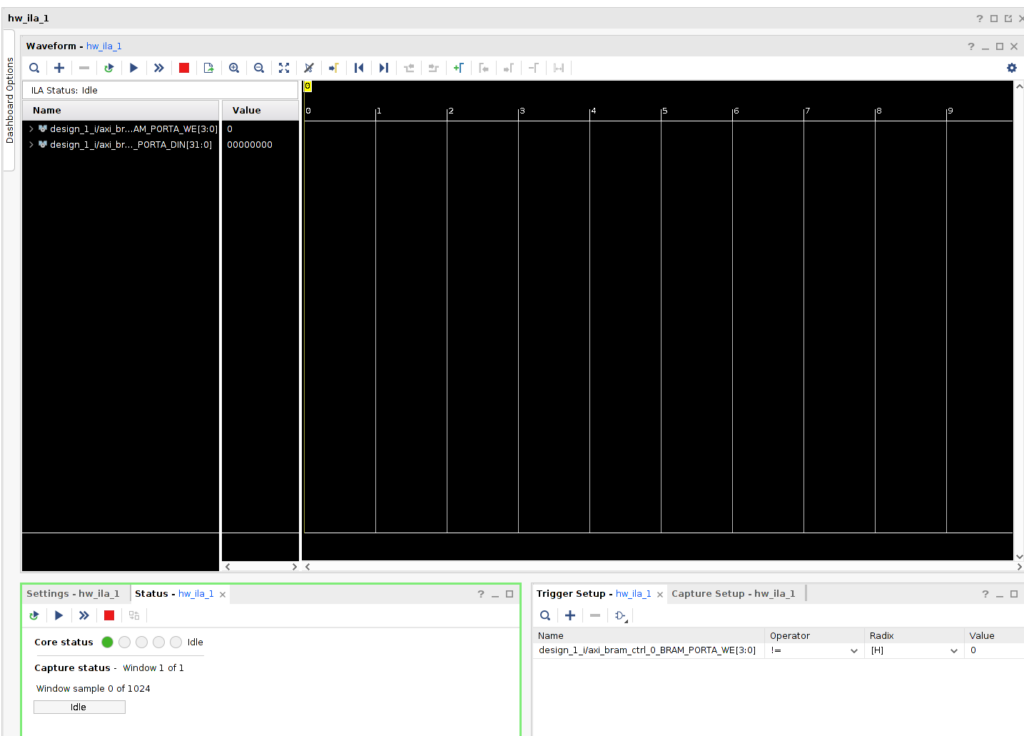

そうすると、ilaの画面がでてくるはずだ。

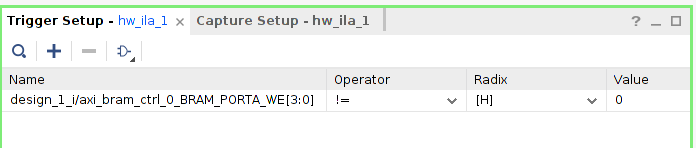

次に、右下のTrigger Setupで、+のボタンを押して、WEBを選択して、Value を0 Operatorを!=にして、WEBが0以外になったら、観測するようにする。

つまり、block memory にライトした時に波形を観測する

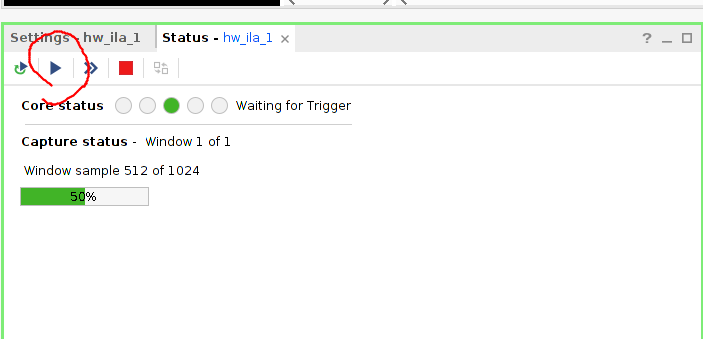

そして、Settings hw_ilaのところで、再生ボタンをクリックする。そうすると、WEBが0以外になるまで、まってくれる。

Vitisを再度動かす

次に、Vitis側で、プログラムを再開する。resumeボタンをクリックする

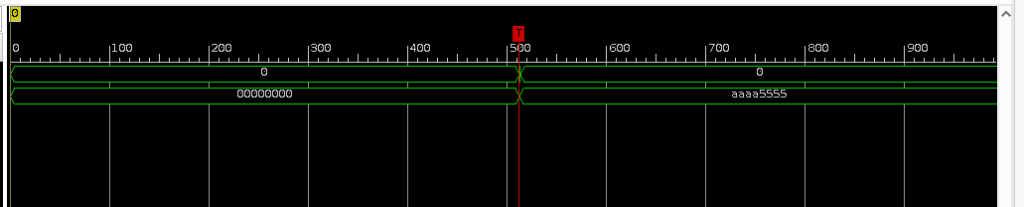

そうすると、Vivado側のILAが反応して、Block Memoryにライトする箇所を観測してくれているはずだ。

しかし、よく見ると、Block Memroyのクロックと、ILAのクロックが同じクロックなので、WE自体が正しく観測できていない。上がWEBで、下がDINAだ。

Blcok Memroyのクロックを遅くするか、もう少し早いクロックで、ILAを観測する必要がありそうだ。