ZynqのCPUから、Block Ramを使用したことがあったが、Verilogから、Block Ramを利用したことがなかった気がしたので、実装してみた。

イメージは、CPUからBlock ramにライトした値を、Calculation(Verilog)からBlock Ramを読み出して、計算してBlock Ramに戻す。そして、CPUで結果をBlock Ramから読み取る。

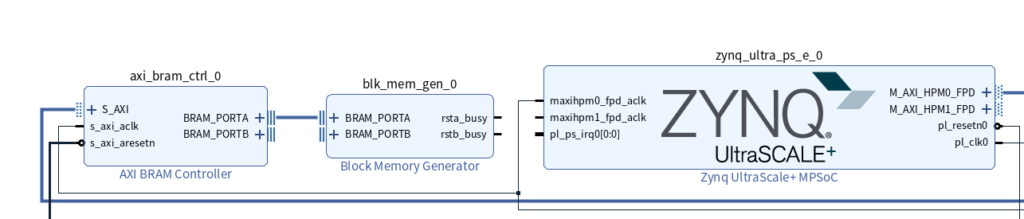

最初に、CPUからBlock Ramを接続する部分を説明する。これらは、XilinxのIPになる。

- Zynq Ultra Scale+ MPSoC:CPU ARMのモジュール

- Block Memory Generator:Blcok Ram

- AXI BRAM Controller:AXIでBlock Ramに接続するモジュール。CPUと接続するために必要

Block Memory Generatorは、Calculation(Verilog)と接続するので、プロパティを開いて、True Dual RAMに変更する。

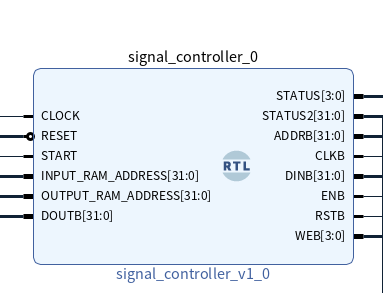

次に、Calculationのモジュールだ。これは自作モジュールだ。

Block Ramの接続部分と、Block Ramの制御指示を受け付ける部分がある。

Block Ramの接続部分は、以下の信号を用意した。詳細は、PG058を読むのが良いと思う。

- DOUTB

- ADDRB

- CLKB

- DINB

- ENB

- RSTB

- WEB

制御指示を受けるのは、以下の信号だ。

- CLOCK:動作クロック

- RESET:リセット

- START:計算開始の指示

- INPUT_RAM_ADDRESS:Bramから読み取るアドレス

- OUTPUT_RAM_ADDRESS:計算結果を書き込むアドレス

- STATUS:デバック情報

- STATUS2:デバック情報

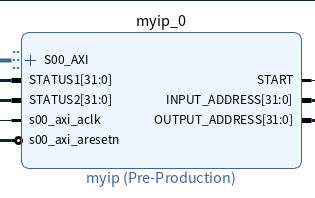

次に、CPU(Zynq)から指示を受けて、Calculationに指示をするモジュール。これも自作モジュールだ。

これは、レジスタを持っている。以下のレジスタを、持つ。

- START指示

- RAM読み込みアドレス

- RAM書き込みアドレス

- ステータス1

- ステータス2

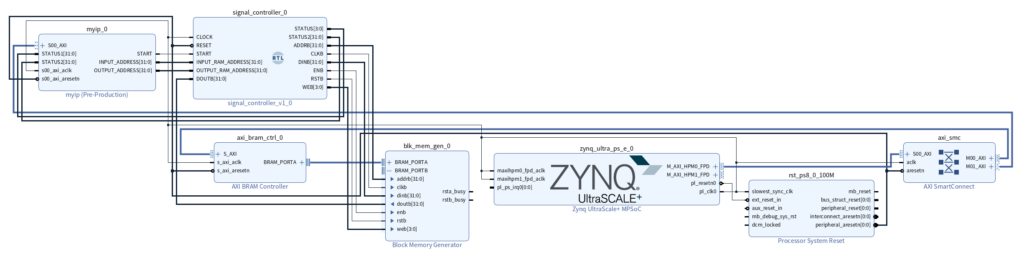

全体を見るとこんな感じだ。

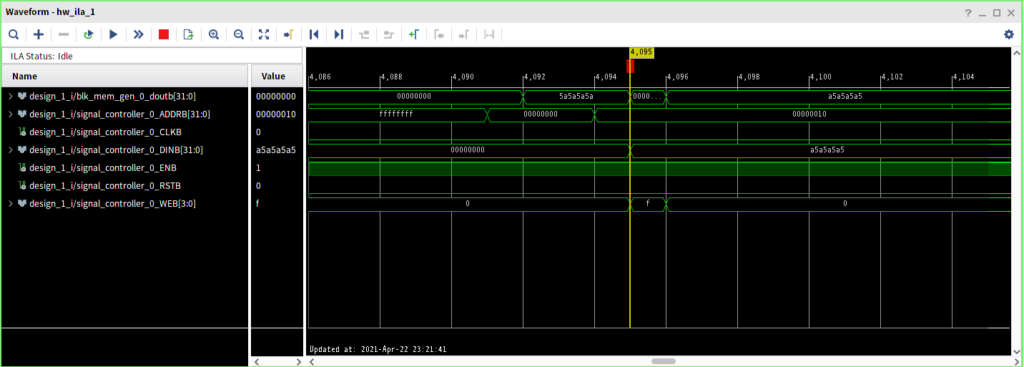

Calclationのbramの部分のリードライト部分の波形を示しておく。

使用したソフトウェアと、Vivadoの環境は、以下においてある