今回は、AXI Verification IPのREADYを制御する方法について記載する。

blogを書くにあたって、以下のサイトを参考にさせてもらった。m(_ _)m

FPGAの部屋

https://marsee101.blog.fc2.com/blog-entry-3790.html

Qiitaの記事

https://qiita.com/tethys_seesaa/items/9d4c00212d9ea79b1497

https://qiita.com/HoriThe3rd/items/03efbc37aa44eb2d2088

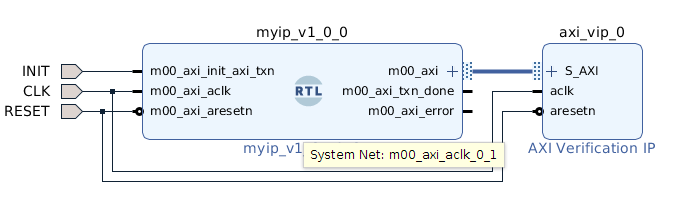

作成したブロック図です。Slave側が、Verification IPを使用している。

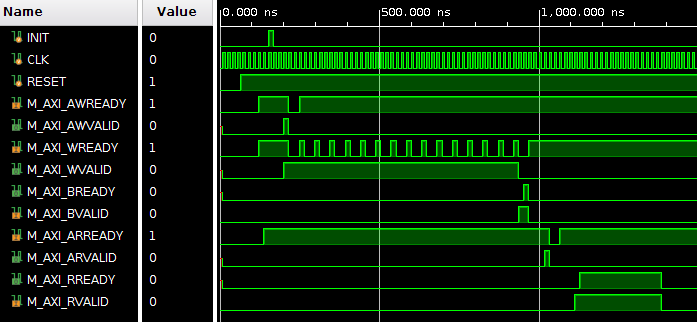

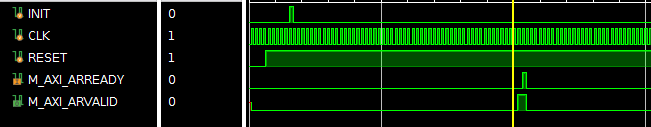

何も設定しない時のタイミングチャートになる。Slave側が発行するREADYは、Verification IP側が先に発行している。

M_AXI_AWREADY、M_AXI_WREADY、M_ARREADYは先に発行されている。

READYを制御するためには、以下のARに添付されているVIPのドキュメントを読む必要がありそうだ。

https://japan.xilinx.com/support/answers/68234.html

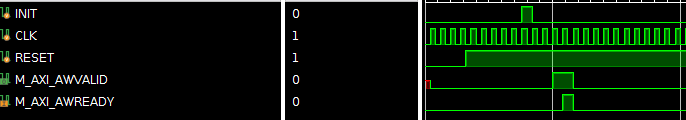

AWREADYを遅延させる方法

set_ready_policyを設定して、send_awready()をコールする

design_1_axi_vip_0_0_slv_mem_t agent;

agent = new("slave vip mem agent",dut.design_1_i.axi_vip_0.inst.IF); // agent is newed

gent.start_slave();

axi_ready_gen wready_gen;

wready_gen = agent.wr_driver.create_ready("ready");

wready_gen.set_ready_policy(XIL_AXI_READY_GEN_AFTER_VALID_SINGLE);

wready_gen.set_low_time(1);

wready_gen.set_high_time(2);

agent.wr_driver.send_awready(wready_gen);

タイミングチャートを見ると、AWREADYがVALIDがでてからHighになっていることがわかる。

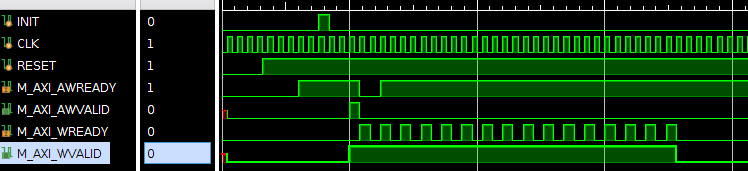

WREADYを遅延させる方法

set_ready_policyを設定して、send_wreadyをコールする

design_1_axi_vip_0_0_slv_mem_t agent;

agent = new("slave vip mem agent",dut.design_1_i.axi_vip_0.inst.IF); // agent is newed

agent.start_slave();

axi_ready_gen wready_gen;

wready_gen = agent.wr_driver.create_ready("awready");

wready_gen.set_ready_policy(XIL_AXI_READY_GEN_AFTER_VALID_SINGLE);

wready_gen.set_low_time(1);

wready_gen.set_high_time(2);

agent.wr_driver.send_wready(wready_gen);

タイミングチャートをみると、WVALIDがHighになってから、WREADYがHighになっていることがわかる。

ARREADYを遅延させる方法

コードです。

design_1_axi_vip_0_0_slv_mem_t agent;

agent = new("slave vip mem agent",dut.design_1_i.axi_vip_0.inst.IF); // agent is newed

agent.start_slave();

axi_ready_gen arready_gen;

arready_gen = agent.rd_driver.create_ready("ready");

arready_gen.set_ready_policy(XIL_AXI_READY_GEN_AFTER_VALID_SINGLE);

arready_gen.set_low_time(1);

arready_gen.set_high_time(2);

agent.rd_driver.send_arready(arready_gen);

次は、Validを出すタイミングを変更したかったが。。。。それはわからなかったっす。

使用したプロジェクトとコードは、以下においてあります。