ultra96で、vioのテストをした。vioは簡単に扱えると聞いたので、試してみました。

最初は、ultra96のチュートリアルベースに、ZYNQを追加します。

https://www.element14.com/community/docs/DOC-91053/l/01ultra96vivadointro2018201zip

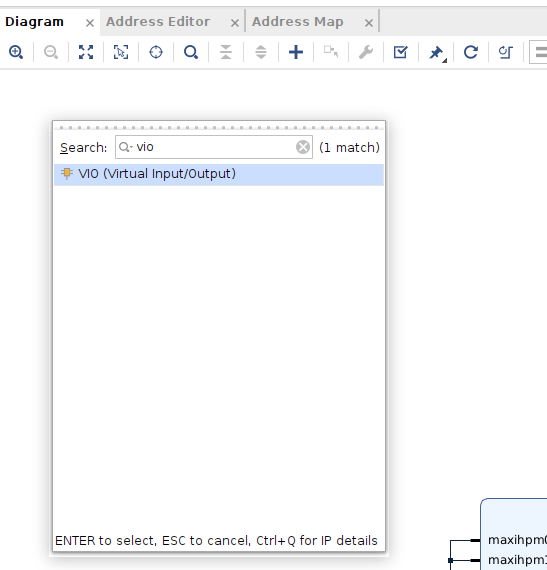

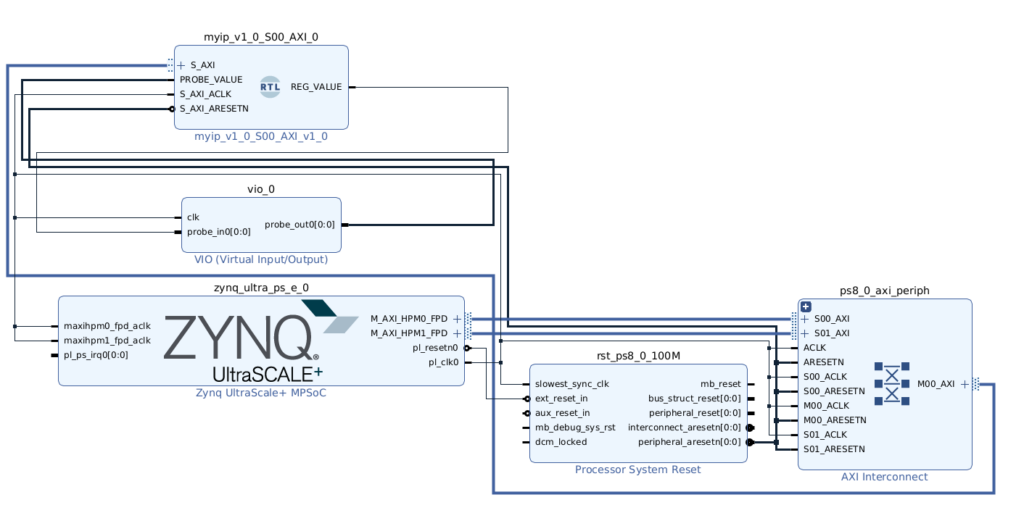

そして、Add IPから VIO (Virtual input/output)を検索して、追加します。

今回は、2つのレジスタを作成します。

・レジスタに1ライトしたら、input probeが1になる

・output probeを1にしたら、レジスタが1になる。

AXI Liteのテンプレートに、外部入出力を追加します。

- // Users to add ports here

- output wire REG_VALUE,

- input wire PROBE_VALUE,

- // User ports ends

1ライトしたら、REG_VALUEを出力します。

- // Add user logic here

- reg reg_value;

- always @( posedge S_AXI_ACLK )

- begin

- if ( S_AXI_ARESETN == 1'b0 ) begin

- reg_value <= 1'b0;

- end else begin

- if (slv_reg0[0] == 1'b1) begin

- reg_value <= 1'b1;

- end else begin

- reg_value <= 0'b0;

- end

- end

- end

- assign REG_VALUE = reg_value;

- // User logic ends

次に、レジスタの値を出力します。レジスタの値を更新している箇所で、レジスタの値を出力します。

- end else begin

- slv_reg1[0] <= PROBE_VALUE;

- end

できたIP(myip)をブロックデザインに追加して、probeと接続します。

そして、GenerateBitStreamを実行します。

次に、ソフトウェアですが、10秒間隔で、レジスタを1→0に変化するソフトと、10秒間隔で、レジスタをリードするソフトウェアを作成します。

- print(“Hello World\n\r”);

- u32 * ptr = 0xa0000000;

- *ptr = 0x1;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x0;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x1;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x0;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x1;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x0;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x1;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- *ptr = 0x00;

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- sleep(10);

- ptr = 0xa0000004;

- for(;;) {

- sleep(10);

- xil_printf(“%x %x\n\r”, ptr, *ptr);

- }

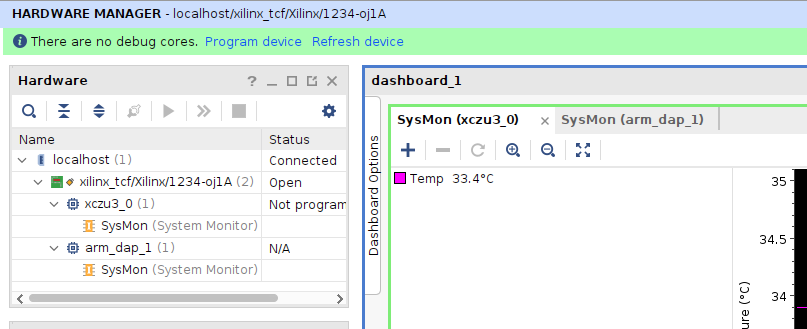

実行します。実行時は、VitisでRunすると、program FPGAも実行してくれるので、VitisでRun して、Vivadoで、Refresh Deviceを実行するのが良いと思います。

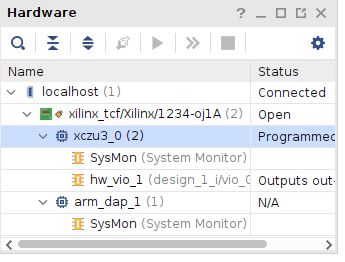

Refresh Deviceを実行すると自動で、hw_vio_1が現れる。

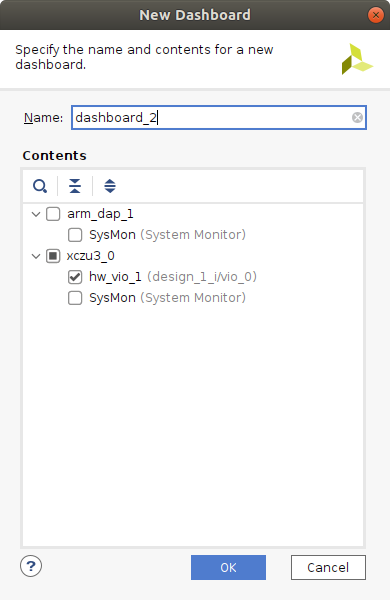

hw_vio_1をダブルクリックすると、dashboard追加の画面がでるので、OKで、追加する。

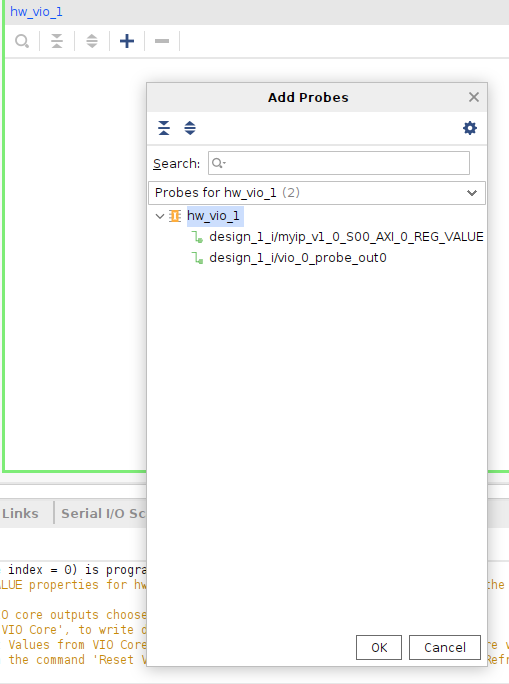

追加DashBoard上で、+ボタンを押して、観測するProbeを選択する。

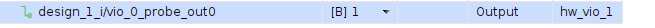

追加したら、outのprobe側は、0と1が選択できるようになる。

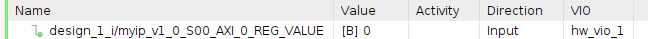

input側は、ソフトウェアの結果に応じて、0⇔1の変化がおきる。output側は、probeの値を変化させると、ソフトの実行結果が変化するはずだ。

0xa0000000が、inputのprobeに接続されていて、0xa0000004がouputのprobeに接続されている。

以下に、FPGAとソフトウェア環境をおいておくー。

https://github.com/y38y38/fpga/tree/master/vio_test

説明は省略しているので、詳細な手順が知りたい方は連絡ください!